电子系团队揭示新兴架构芯片弱一致性缓存的侧信道安全问题

新清华 2025年10月31日 第2380期 学术前沿

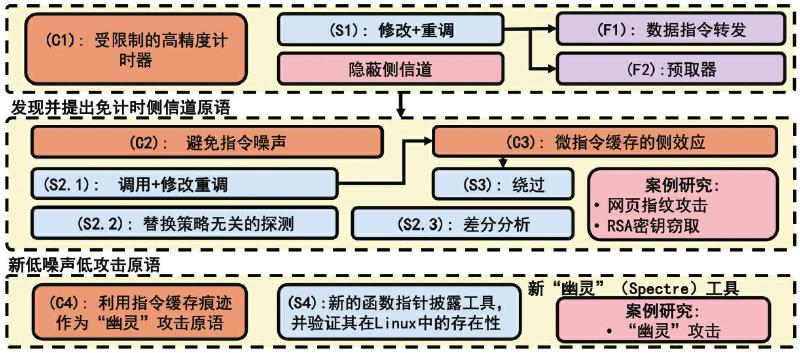

强弱一致性缓存相关机制逆向与利用。

本报讯 在集成电路全球化与处理器架构快速演进的背景下,芯片微架构层面的隐私与安全问题始终是硬件系统设计中的关键挑战。随着RISC-V等新兴指令集架构的发展与普及,处理器在高能效与开放性上优势显著,但其微架构的新特性也带来了新的攻击面和潜在风险。传统侧信道攻击通常依赖高精度计时指令进行信息提取。近年来,处理器通过限制计时器访问以缓解此类威胁。然而,在新兴微架构机制下,仍不确定这些防御措施能否真正消除缓存层的隐私泄露风险。因此,开展预防性的微架构分析、逆向与漏洞挖掘研究,对于保障处理器体系安全至关重要。

近日,电子系刘勇攀、杨华中教授团队在免计时缓存侧信道安全方向取得重要研究进展。研究通过对多个不同架构的芯片的微架构特性开展的系统性安全分析发现,新兴商用与开源架构芯片中普遍部署了弱一致性一级缓存,攻击者可利用这一特性,绕过现有安全限制,构造免定时器与计数器的缓存攻击。

基于上述发现,团队提出了新的攻击GhostCache(幽灵缓存),并在多个RISC-V与ARM的商用与开源芯片上完成系统性实验验证,揭示了弱一致性缓存架构下的安全隐患。基于GhostCache,团队构建了三类跨安全区域的隐蔽信道,实现了跨线程、跨特权级甚至跨核心的信息传输。该机制进一步被应用于多种攻击场景中,包括内核数据泄露与加密密钥窃取。在实际侧信道利用层面,研究实现了三类典型攻击验证:网页指纹识别攻击,即在ARM与RISC-V芯片上均可实现免定时器的浏览器硬件缓存状态监测,100类网站缓存指纹分类准确率超过90%;内核数据泄露攻击,即包括对内核条件分支执行路径的重建和Spectre瞬态执行攻击,团队基于Linux内核中发现的函数指针调用,构造了首个基于指令缓存的Spectre泄露工具;RSA密钥窃取攻击,即利用现代密码算法库中关键路径的条件分支导致的指令缓存侧信道完成密钥重构。

研究提出的GhostCache,不仅揭示了弱一致性架构下的新缓存侧信道风险,也为后续的安全防御研究提供了新的关注点。团队发现的安全问题,是国内首次在商用处理器上发现并披露的免计时缓存侧信道攻击案例,该成果得到业界包括ARM安全团队在内的广泛认可及开源领域香山团队的感谢。

研究成果以“GhostCache:利用RISC-V和ARM芯片的弱一致性缓存的免计时和计数的缓存攻击”为题,被第32届计算机与通信安全会议接收。该会议是信息安全领域水平最高、影响力最强的国际顶级学术会议之一。

电子系助理教授邓舒文为该论文的通讯作者,电子系2025级博士生金宇为第一作者。

(电子系)